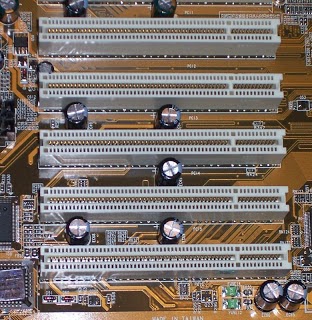

PCI (Peripheral

Component Interconnect) merupakan bus yang tidak tergantung prosesor dan

berbandwidth tinggi yang dapat berfungsi sebagai bus mezzanine atau bus

peripheral dibandingkan dengan spesifikasi bus

lainnya. Peripheral yaitu peralatan- peralatan di luar sistim

mikrokomputer yang dapat berhubungan dengan sistim mikrokomputer, antara

lain monitor (output), printer (output), keyboard (input), mouse

(input).

PCI memberikan sistem yang lebih baik bagi subsistem

I/O berkecepatan tinggi (misalnya: graphic display adapter, network

interface controller, disk cotroller, dll). Standar yang berlaku saat

ini mengizinkan pengunaan sampai 64 saluran dan pada kecepatan 33 MHz,

bagi kelajuan transfer 264 Mbyte/detik, atau 2,112 Gbps. Namun bukan

hanya kecepatannya saja yang tinggi yang membuat PCI menarik, PCI khusus

dirancang untuk memenuhi kebutuhan I/O sistem yang modern secara

ekonomi. PCI hanya memerlukan keping yang lebih sedikit untuk

mengimplementasikan dan mendukung bus lainnya yang dihubungkan ke bus

PCI.Intel mulai menerapkan PCI pada tahun 1990 untuk sistem berbasisi pentiumnya. Segera Intel menerbitkan semua patent bagi domain publik dan mempromosikan pembuatan himpinan industri, PCI SIG, untuk pembuatan lebih lanjut dan memelihara kontabilitas spesifikasi PCI. Hasilnya adalah bahwa PCI secara luas diterima dan penggunaannya pada komputer pribadi, workstasion, dan sistem server terus meningkat. Versi saat ini, PCI 2.0. diterbitkan 1993. karena spesifikasinya berada di dalam domain publik dan didukung oleh industri microprocessor dan peripheral secara luas, PCI yang dibuat oleh vendor yang berlainan tetap kompatibel.http://www.adhitsblog.com/2014/04/apa-arti-pci.html

PCI dirancang untuk mendukung bermacam-macam konfigurasi berbasis mikroprosesor, baik sistem microprosesor tunggal maupun banyak. Karena itu, PCI memberikan sejumlah fungsi untuk kebutuhan umum. PCI memanfaatkan timing sinkron dan pola arbitrasi tersentralisasi. Kombinasi pengontrol DRAM dan bridge dengan bus PCI memberikan coupling yang erat dengan prosesor dan kemampuan pengiriman data berkecepatan tinggi. Bridge berfungsi sebagai suatu buffer data sehingga kecepatan bus PCI berbeda dengan kemampuan I/O prosesor. Fungsi bridge yang menjaga agar PCI tidak tergantung pada kecepatan prosesor memberikan kemampuan untuk menerima dan mengirimkan data secara cepat.

Struktur Bus

PCI dapat dikonfigurasikan sebagai bus 32-bit atau 64-bit. Signal-signal yang diharuskan bagi PCI dibagi menjadi kelompok-kelompok fungsional sebagai berikut:

1. System pins:

Meliputi pin waktu dan pin reset.

2. Address dan Data Pins:

Meliputi 32 saluran yang time-multiplexed bagi alamat data. Saluran lainnya di dalam kelompok ini digunakan untuk menginterpretasi dan memvalidasi saluran-saluran signal yang membawa alamat dan data.

3. Interface Control Pins:

Mengotrol timing transaksi dan mengkoordinasikan antara inisiator dan target.

4. Arbitration Pins:

Tidak seperti saluran signal PCI lainnya, pin-pin ini bukan saluran yang dipakai bersama-sama. Melainkan masing-masing master PCI memiliki pasangan saluran arbitrasinya sendiri yang menghubungkannya secara langsung dengan arbiter bus PCI.

5. Error Reporting Pins:

Digunakan untuk melaporkan error parity dan error-error lainnya.

Selain itu, spesifikasi PCI mendefinisikan 50 saluran signal optimal yang dibagi menjadi kelompok-kelompok fungsional sebagi berikut:

1. Interrupt Pins:

Saluran signal ini disediakan bagi perangkat-perangkat PCI yang harus menghasilkan request untuk layanan. Seperti halnya arbiterasi, pin-pin ini pun bukan saluran yang dapat dipakai bersama. Melainkan masing-masing perangkat PCI memiliki sendiri saluran interrupt ke pengpntrol interrupt.

2. Cache Support Pins:

Pin-pin ini diperlukan untuk mendukung memori pada PCI yang dapat di-cache-kan di dalam prosesor atau perangkat lainnya. Pin-pin ini mendukung protokol-protokol snoopy cache.

3. 64-bit Bus Extension Pins:

Meliputi 32 saluran yang merupakan time-multiplexed bafi alamat dan data dan dikombinasikan degab saluran alamat atau data untuk membentuk bus alamat/data 64-bit. Saluran lainnya di dalam kelompok ini digunakan untuk menginterpretasi dan memvalidasi saluran-saluran signal yang membawa alamat/data. Terakhir, terdapat dua saluran yang memungkinkan dua perangkat PCI untuk menyetujui penggunaan kemampuan 64-bit.

4. JTAG/Boundary Scan Pins:

Saluran-saluran signal ini mendukung pengujian prosedur-prosedur yang ditentukan dalam standard 149.1 IEEE.

Perintah-perintah PCI

Aktivitas bus terjadi dalam bentuk transaksi antara sebuah mistator, atau master dengan sebuah target. Ketika mempperoleh kontrol bus , master bus menentukan jenis transaksi yang akan terjadi berikutnya. Selama fase alamat dari suatu transaksi, saluran C/BE dipakai untuk memberikan signal tenis transaksi. Perintah-perintah itu adalah:

1. Interrupt Acknowledge

Adalah perintah baca yang ditujukan bagi perangkat yang berfungsi sebagai pengotrol interrupt pada bus PCI. Saluran alamat tidak digunakan sekama fase alamat, dan saluran byte enable menunjukkan ukuran interrupt identifier untuk dikembalikan.

2. Special Cycle

Digunakan oleh inisiator untuk melakukan broadcast pesan ke sebuah target atau lebih.

3. I/O Read dan I/O write

Digunakan untuk melakukan transfer data antara inisiator dengan pengontrol I/O. setiap alamat I/O memiliki ruang tersendiri, dan saluran alamat digunakan untuk menunjukkan perangkat tertentu dan untuk menspesifikasikan data yang akan ditransfer ke perangkat itu atau ditransfer dari perangkat tersebut.

4. Memori read dan write

Digunakan untuk menspesifikasikan transfer data, yang menempati satu siklus waktu atau lebih. Interpretasi perintah-perintah ini tergantung pada apakah pengontrol memori pada bus PCI mendukung protokol PCI untuk trasfer antara memori dengan cache atau tidak. Perintah Memory Write dipakai untuk mentransfer data dalam satu siklus waktu atau lebih ke memori.

5. Memory Write and Invalidate

Mentransfer data dalam satu siklus waktu atau lebih ke memori. Selain itu, perintah ini menjamin bahwa sedikitnya satu saluran cache akan ditulis. Perintah ini mendukung fungsi cache tentang penulisan kembali saluran ke memori.

6. Configuration Read dan Write

Kedua perintah konfigurasi memungkinkan suatu master membaca dan meng-update parameter-parameter konfigurasi pada perangkat yang terhubung ke PCI. Masing-masing perangkat PCI dapat meliputi hingga 256 buah register internal yang digunakan selama inisialisasi sistem untuk mengkonfigurasi perangkat itu.

7. Dual Address

Digunakan oleh inisiator untuk menunjukkan bahwa inisiator memakai pengalamatan 64 bit.

Transfer Data

Setiap transfer data pada PCI merupakan transaksi tunggal yang terdiri dari sebuah fase alamat dan satu atau lebih fase data. Berikut akan dijelaskan mengenai timing transakasi pembacaan. semua kejadiannya disinkronkan dengan transaksi balik pewaktu, yang terjadi di tengah-tengah pada setiap siklus waktu. Perangkat bus men-sample saluran bus pada ujung yang naik pada awal siklus bus. Berikut adalah kejadian-kejadian penting yang diberikan sebagai label pada diagram:

1. Sekali master bus telah memperoleh kontrol bus, maka master bus akan memulai transaksi dengan menegaskan FRAME. Saluran ini akan tetap ditegaskan sampai inisiator siap untuk menyelesaikan fase data yang terakhir. Inisiator juga menaruh alamat awal pada bus alamat, dan membaca perintah pada saluran C/BE.

2. Pada awal waktu ke-2, perangkat target akan mengetahui alamatnya di saluran AD.

3. Inisiator berhenti mengendalikan bus AD. Siklus baik(turnaround) diperlukan pada semua saluran signal yang akan dikendalikan oleh lebih dari sebuah perangkat, sehingga penurunan signal alamat akan mempersiapkan bus untuk dipakai oleh perangkat target. Inisiator mengubah informasi pada saluran C/BE untuk memilih saluran AD yang akan digunakan untuk melakukan transfer data beralamat (dari 1 hingga 4 bit) saat itu. Inisiator juga menegaskan IRDY untuk menandakan bahwa dirinya siap untuk butir data pertama.

4. Target yang termilih menunjuk DEVSEL, untuk menunjukkan bahwa target telah mengetahui alamatnya dan akan memberikan respon. Target yang terpilih menempatkan data yang diminta pada saluran AD dan menegaskan TRDY untuk mengindikasikan bahwa data yang valid terdapat pada bus.

5. Inisiator membaca data pada awal waktu ke-4 dan mengubah saluran enable byte, begitu diperlukan dalam persiapan pembacaan berikutnya.

6. Dalam contoh ini, target membutuhkan beberapa saat untuk mempersiapkan blok kedua ntuk transmisi. Karena itu target melepaskan TRDY untuk memberi signal kepada inisiator bahwa tidak akan terdapat data baru selama sklus berikutnya. Kemudian inisiator tidak akan membaca saluran data pada awal siklus waktu ke-5 dan tidak mengubah byte enable selama siklus itu. Blok data dibaca pada awal waktu ke-6.

7. Selama waktu ke-6, target menempatkan butir data pada bus. Namun dalam contoh ini, inisiator belum siap untuk membaca butir data (misalnya inisiator mempunyai kondisi penuh buffer sementara). Karena itu inisiator melepaskan IRDY. Hal ini akan menyebabkan target untuk menyediakan butir data ketiga pada bus siklus waktu tambahan.

8. Inisiator mengetahui bahwa transfer data ketiga adalah yang terakhir, karena itu inisiator melepaskan FRAME untuk memberikan signal ke target bahwa itu merupakan transfer data yang terakhir. Inisiator juga melepaska IRDY untuk memberikan signal bahwa dirinya siap untuk menyesaikan transfer tersebut

9. Inisiator melepaskan IRDY, yang mengembalikan bus ke dalam idle, dan target melepaskan TRDY dan DVSEL.

D. Arbitrasi

PCI memafaatkan pola arbitrasi sentral dan singkron yang masing-masing masternya memiliki request unik (REQ) dan signal (GNT). Saluran-saluran signal ini dihubungkan dengan arbiter sentral request grant handshake sederhana digunakan untuk memberikan akses ke bus.

Spesifikasi PCI tidak memharuskan arbitrasi. Arbiter dapat menggunakan pendekatan first-come-firtsserver, pendekatan round-robin, atau pola prioritas lainnya. Master PCI harus mengarbitrasi setiap transaksi yang ingin dibentuknya, yaitu sebuah transaksi terdiri dari sebuah fase alamat yang diikuti oleh satu fase data kontigus atau lebih. Ketika sebuah perangkat A dan B melakukan arbitrasi untuk bus, langkah-langkah yang terjadi adalah sebagai berikut:

1. Pada suatu titik sebelum awal waktu ke-1, A telah menegaskan signal REQ-nya. Arbitrer mensample signal ini pada awal siklus waktu ke-1.

2. Selama siklus waktu ke-1, B membuat request untuk menggunakan bus dengan menegaskan signal REQnya.

3. Pada saat yang sama, arbiter menegaskan GNT-A untuk memberikan hak akses bus kepada A.

4. Master bus A men-sample GNT-A pada awal waktu ke-2 dan memeriksa apakah dirinya telah diberi hak mengakses bus. Master bus juga menemukan pelepasan IRDY dan TRDY yang menandakan bahwa bus tersebut dalam keadaan idle. Selain itu, master bus menegaskan FRAME dan menempatkan informasi alamat pada bus alamat dan perintah pada bus C/BE. Master bus juga melanjutkan penegasan REQ-A, karena master bus memiliki transaksi kedua yang akan dibentuk setelah transaksi ini.

5. Arbitrer bus men-sample semua saluran GNT pada awal waktu ketiga dan membuat keputusan arbitrasi untuk memberikan hak mengakses bus ke B pada transaksi beriknya. Kemudian arbitrer bus menegaskan GNT-B dan melepaskan GNT-A. B tidak akan dapat menggunakan bus hingga bus itu dikembalikan ke keadaan idle.

6. A melepaskan FRAME untuk menandakan bahwa transfer data terakhir sedang dilakukan. A menaruh data pada bus data dan memori signalke target dengan IRY. Target membaca data pada awal siklus waktu berikutnya.

7. Pada awal waktu ke-5, B menemukan IRDY dan FRAME yang dilepaskan dan karena itu B dapat melakukan kontrol terhadap bus dengan menegaskan FRAME. B juga melepaskan saluran REQnya karena B hanya perlu membentuk satu transaksi saja.

Perkembangan PCI

Spesifikasi bus PCI pertama kali dirilis pada bulan Juni 1992, sebagai PCI vesi 1.0. Perkembangan selanjutnya dapat dilihat pada tabel berikut.

Spesifikasi bus PCI Dirilis pada Perubahan yang dilakukan

PCI 1.0 Juni 1992 Spesifikasi asli PCI, yang memiliki lebar bus 32-bit atau 64-bit

PCI 2.0 April 1993 Spesifikasi ini mendefinisikan jenis konektor dan papan ekspansi

PCI 2.1 Juni 1995 Operasi 66 MHz diberlakukan; Perubahan pada latency; Adanya fungsi transaction ordering

PCI 2.2 Januari 1999 Fitur manajemen daya diberlakukan; Ada beberapa klarifikasi mekanika

PCI-X 1.0 September 1999 Spesifikasi PCI-X 133 MHz, sebagai tambahan bagi versi PCI 2.2

Mini-PCI November 1999 Spesifikasi PCI 2.2 untuk motherboard dengan form factor yang kecil (Micro-ATX)

PCI 2.3 Maret 2002 Pensinyalan 3.3 Volt; Penggunaan kartu yang bersifat low-profile

PCI-X 2.0 Juli 2002 Modus kerja 266 MHz dan 533 MHz; dukungan terhadap pembagian bus 64-bit menjadi segmen-segmen berukuran 16-bit atau 32-bit; Pensinyalan 3.3 Volt atau 1.5 Volt.

PCI Express 1.0 Juli 2002 PCI dengan cara transmisi serial, dengan kecepatan 2500Mb/s tiap jalur transmisi tiap arah, menggunakan pensinyalan 0.8 Volt, sehingga menghasilkan bandwidth kira-kira 250MB/s tiap jalurnya; Didesain untuk menggantikan PCI 2.x dalam sistem PC.

So, kesimpulannya fungsi dari Slot PCI adalah tempat/slot untuk modem,tv tuner,LAN card(Multi Fungsi)

Tidak ada komentar:

Posting Komentar